_@¡ použijte menu „FILTROVAT TÉMA...“ pro výběr

Zadání

Na vstupu detekuji audiosignál, pokud přichází déle než určitou dobu (alespoň několik sekund), tak dojde k zapnutí audio zesilovače, pokud signál ustane, tak po delší době (např. 10min) bude zesilovač vypnut. Takto dlouhý čas je zde proto, že zapínám a vypínám elektronkový zesilovač a nechci zbytečně často vypínat/zapínat žhavení.

1) Řešení USB spínané relé

Pokud bude zdroj audiosignálu počítače, tak by přímo operační systém měl vědět, zda nějaký zvvuk ven jde a nebo ne a pokud bude mít počítač možnost nějak sepnout relé pro zapnutí zesilovače, tak to vyřešit půjde.

[modul] relé ovládaný z USB

Software je k dispozici, nabízí možnost něco snadno spínat přímo z počítače. Tedy pro aplikaci – když to hraje zapni zesilovač – použitelné. Jak zjistit, zda počítač zrovna něco hraje? Pro Windows jen nápad: příkaz powercfg /request vrací něco jako:

EXECUTION:

[PROCESS] \Device\HarddiskVolume4\Program Files (x86)\Google\Chrome\Application\chrome.exe

Playing audio

nebo

EXECUTION:

[PROCESS] \Device\HarddiskVolume4\Users\uzivatel\AppData\Roaming\Spotify\Spotify.exe

Background Audio Playback

a dotaz:

powercfg /requests | findstr -i audio

vrácí neprázdný řádek, pokud nějaké audio blokuje možnost uspání počítače...

Ne vždy je zdrojem zvuku právě počítač a hledám víc univerzální řešení. Jak detekovat audiosignál nejen z počítače.

2) Řešení s Arduinem a programem

Obecný zdroj audiosignálu – a tím chceme zapnout zesilovač – potřebujeme měřit, zda v audiokabelu je nějaký signál, který není šum a řídit se podle něj.

Arduino[1] nebo stačí i Digispark[2] s malinkým procesorem Attiny85. Na vstup A0 bude přiveden audiosignál z počítače – sluchátkový výstup – takový signál může být velmi slabý a pro zapnutí zesilovače by měl stači i signál třeba jen deset milivoltů.

Analogově digitální převodník Arduina převede signál o napětí 0–5V na číselnou hodnotu 0–1023. To vychází při 4,89mV na jeden krok. Tedy hodnota 5mV je nedetekovatelná a myslím, že i hodnota kolem 20mV se bude detekovat obtížně.

Potřebujeme tedy vstupní signál zesílit

K tomu poslouží modul operačního zesilovače, zesílení až 100×

[modul] XD-21 za 1€

Jak [funguje]

Nebo třeba jednoduchý jednotranzistorový zesilovač, který udělá podobnou práci.

Výstup takového zesilovače je kladný i záporný, proto se musí připojit do středu refenčního napětí. Ale lze to i zjednodušit a zapojit to alespoň takto, opět do středu 2,5V.

Máme-li potřebné zesílení, aby se dal signál rozumně detekovat vůči referenčnímu napětí 5V, můžu připojit analogový vstup. Pro nastavení citlivosti programu můžeme nastavit hodnotu přímo v programu nebo připojit trimr na analogový vstup A1 a měnit citlivost bez nutnosti měnit program.

Nemůžu zapnout zesilovač ihned po detekci signálu. Aby se nezapínal kvůli nějakému náhodnému šumu. Musím chvíli signál sledovat a teprve když hraje nějakou dobu, tak teprve dát pokyn ke spuštění.

Zapojení

Pokud napájím Arduino z USB, je potřeba mezi 5V a GND připojit nějaký větší (820µF) kondenzátor, aby aspoň trochu filtroval průběh napětí, protože toto slouží též jako referenční napětí pro analogové vstupy a není vůbec snadné něco měřit, když je reference příliš plave[4].

– A1 – trimr pro nastavení citlivosti zapojený jako napěťový dělič 0–5V

– vestavěná LED bliká při detekci signálu

– D8 – pin ovládající zapnutí/vypnutí SSR relé modulu pro reálné zapnutí zesilovače

Program

Asi lepší než slovní popis, je číst zdrojový kód[5] programu, ale stejně zkusím slovně popsat algoritmus řešení

– přečti napětí na A1 a nastav limity detekce

děje se tak neustále, abych podle problikávání notifikační LED mohl snadno nastavit citlivost při praktickém nasazení; stabilitu, aby se hranice pořád rychle neměnily, zajistí zaokrouhlení čtené hodnoty na násobky dvaceti

– přečti napětí na A0

– pokud je v nastavených limitech

→ tak je to pouze šum

– pokud je detekován signál, který není šum

→ započti detekci a rozviť notifikační LED

– pokud je detekcí dostatek

→ začni měřit čas pro zapnutí

→ vynuluj časovač pro vypnutí

– pokud signál na vstupu není

→ započti absenci a zhasni notifikační LED

– pokud je absencí dostatek

→ začni měřit časovač pro vypnutí

→ vynuluj čas pro zapnutí

– pokud časovač pro zapnutí dosáhl nastaveného limitu (nastaveno 5 vteřin)

→ dej požadavek na zapnutí zesilovače

– pokud časovač pro vypnutí dosáhl nastaveného limitu (10 vteřin při testování, 10 minut v praxi)

→ dej požadavek na vypnutí zesilovače

– opakuj od začátku

Celý odladěný program je [zde]. Snažil jsem se to přehledně okomentovat. Není v něm nic záludného. Všechny parametry se dají změnit jen definicí konstant na začátku.

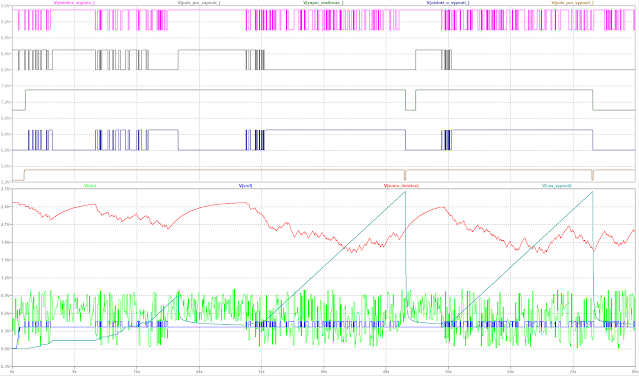

V sériovém plotru je vidět všechny potřebné průběhy. Dá se použít k nastavení středu ADC převodníku a limitů detekce.

Při detekci signálu se rozsvítí vestavěná LED, tedy bez signálu, když je na vstupu pouze šum, který je velmi velmi zesílený, tak by měla LED jen občas probliknout.

S procesorem vyřešeno, funguje spolehlivě s výbornou citlivostí díky zesilovači na vstupu.

3) Řešení bez procesoru

Přemýšlel jsem, jak to řešit bez procesoru. Výše zmíněná „logika programu“ je dodržena, jen to řešení je zajímavější. Napájení z 5V.

Soubory LTSpice ke stažení [zde]. "auto-zapnuti-zesilovace1.asc"

Komparátor LM339 porovnává vstup s referenčním napětím VREF, které se nastavuje pomocí trimru U8 v rozsahu 30mV – 1.7V. Výstup komparátoru U1 nabíjí kondenzátor C4, který slouží jako SUMA_detekce a až dosáhne napětí hranice logické 1, tak invertory U17 nastaví žádost o zapnutí a U18 nastaví puls pro zapnutí na CLK vstup 7474 klopného obvod a ten nastaví zapínací výstup Q na 1 a podrží ho zapnutý celou dobu, dokud nepřijde požadavek na vypnutí (nastavením nulovacího vstupu CLR).

Požadavek na vypnutí je vyhodnocen hradlem NAND U7 7400 jako následující podmínka: Je nastaven požadavek na vypnutí a zároveň je zesilovač zapnutý? Výstup U17 je 0 a výstup Q obvodu U2 je 1. V tom případě se začne proudový zdroj Q2 lineárně nabíjet kondenzátor C6 přes rezistor R16. Nabíjení se může kdykoli přerušit novým požadavkem na zapnutí. Když napětí na kondenzátoru C6 dosáhne hranice logické 1, invertory U5, U6 spolu s NAND hradlem U3 se postarají, ale přišla logická 0 na resetovací vstup CLR klopného obvodu U2, který drží zesilovač zapnutý.

Notifikační LEDky informují o tom, co se zrovna děje.

Dioda D3 zabrání tomu, aby se kondenzátor vybíjel zpátky do celého obvodu. Kondenzátory C4 se vybíjí velmi pozvolna přes R10. C6 má vybíjecí tranzistor Q1 a je vybitý okamžitě, když nabíjecí napětí spadne k logické 0.

graf průběhu obsahuje simulaci 80s, kdy je šum, je signál na vstupu, je zapnuto i vypnuto

v horní části je vidět výstup z logiky HIGH a LOW; shora:

– V(detekce_signalu) na vstupu - když se mění rychle, komparátor se překlápí a detekuje rušení na vstupu - když je HIGH po delší dobu, bylo přičteno 1.5V ze zdroje V2 - zvuk je zapnut

– V(puls_pro_zapnuti) - signál na vstupu byl již dost dlouhou dobu (asi 5s) k tomu, aby se nabil kondenzátor C4 a dosáhl napěťové hodnoty HIGH, která překlopí schmittův obvod v invertoru a poslal puls CLK pro zapnutí přes U17 a U18; puls_pro_zapnutí je „žádost o zapnutí“; pokud není zapnuto, bude zapnuto, pokud zapnuto je, nic se nemění. Pokud zapnuto je a zároveň je dána žádost o vypnutí, tak při dalším pulsu pro zapnutí je tato žádost zrušena

– V(zapni_zesilovac) - překlopení D klopného obvodu U2, přišel puls pro zapnutí a obvod zapne zesilovač a zůstane zapnutý tak dlouho, než přijde puls pro vypnutí

– V(zadost_o_vypnuti) - když signál na vstupu ustane, takže U17 vrací na výstupu logickou jedničku a zároveň je zesilovač zapnutý, tedy U2 má na výstupu Q logickou jedničku, tak NAND hradlo U7 nastaví zadost_o_vypnutí na logickou jedna

– V(puls_pro_vypnuti) - výstup invertoru U4 nabíjí kondenzátor C6 a když napětí na něm dosáhne hodnoty logické jedna, překlopí se schittův invertor U5 a přes U6 a NAND hradlo U3 pošle puls CLR k resetování klopného obvodu, který nastaví svůj výstup V(zapni_zesilovac) na logickou 0 a je připraven přijmout další – V(puls_pro_zapnuti) na svůj CLK vstup a znovu se překlopit.

v dolní části je výstup analogové části schématu:

– V(vin) - šum signálu na vstupu, způsobí občasné překlopení komparátoru a způsobuje neustálé V(detekce_signalu) viditelné v horní části a když se na vstupu objeví silnější signál, V(detekce_signalu)zůstane v logické 1 delší dobu

– V(vref) - referenční napětí na 0.4V pro komparátor

– V(suma_detekce) - pulsy z komparátoru nabíjí kondenátor C4, který se průběžně vybíjí přes R10

– V(cas_vypnuti) - průběh nabíjení kondenzátoru C6, pokud dosáhne napětí na něm hodnoty logické 1, pošle V(puls_pro_vypnuti). Vybije se přes tranzistor Q1 vždy, když V(zadost_o_vypnuti) zmizí a je v logické 0.

Realizace a test

Vstup je stereo, takže dva kanály přes oddělovací kondenzátory jsou smíchány do jednoho a prochází přes jednotranzistorový zesilovač[4]. Zesílení asi 50×. Důležitý je malý kondenzátor mezi bází a kolektorem, který sníží rušení a zajistí, aby zesilovač pracoval pouze v audiopásmu.

Ověřeno, funguje, rozpozná signál od amplitudy 5mV na vstupu. Jako prvotní nápad proč ne, ale chtělo by to malinko vylepšit. Např. C4 (suma detekce) se průběžně vybíjí přes R10 a bylo by lepší vybíjení řídit časově. Ale tohle mě napadlo, až jsem to měl zadrátované. Použít generátor pulsu, který spouští rychlé vybití sumačního kondenzátoru.

V otestovaném zapojení je toto řešení prakticky použitelné. Díky zesílení 50× je vstup opravdu velmi citlivý a díky sumě detekce zároveň zesilovač nevzbudí kdejaký šum. Citlivost jsem nastavil tak, aby při tichu, kdy je na vstupu pouze šum, problikla žlutá detekční LED jen občas.

[youtube] video

K tomuto zadání se ještě vrátím, určitě existují další zajímavá řešení.

Další čtení

[8] včetně simulace

[9] další nápady na stejné téma